- 您现在的位置:买卖IC网 > Sheet目录1991 > CS4341A-KSZ (Cirrus Logic Inc)IC DAC STER 24BIT 192KHZ 16SOIC

CS4341A

6

DS582F2

2.

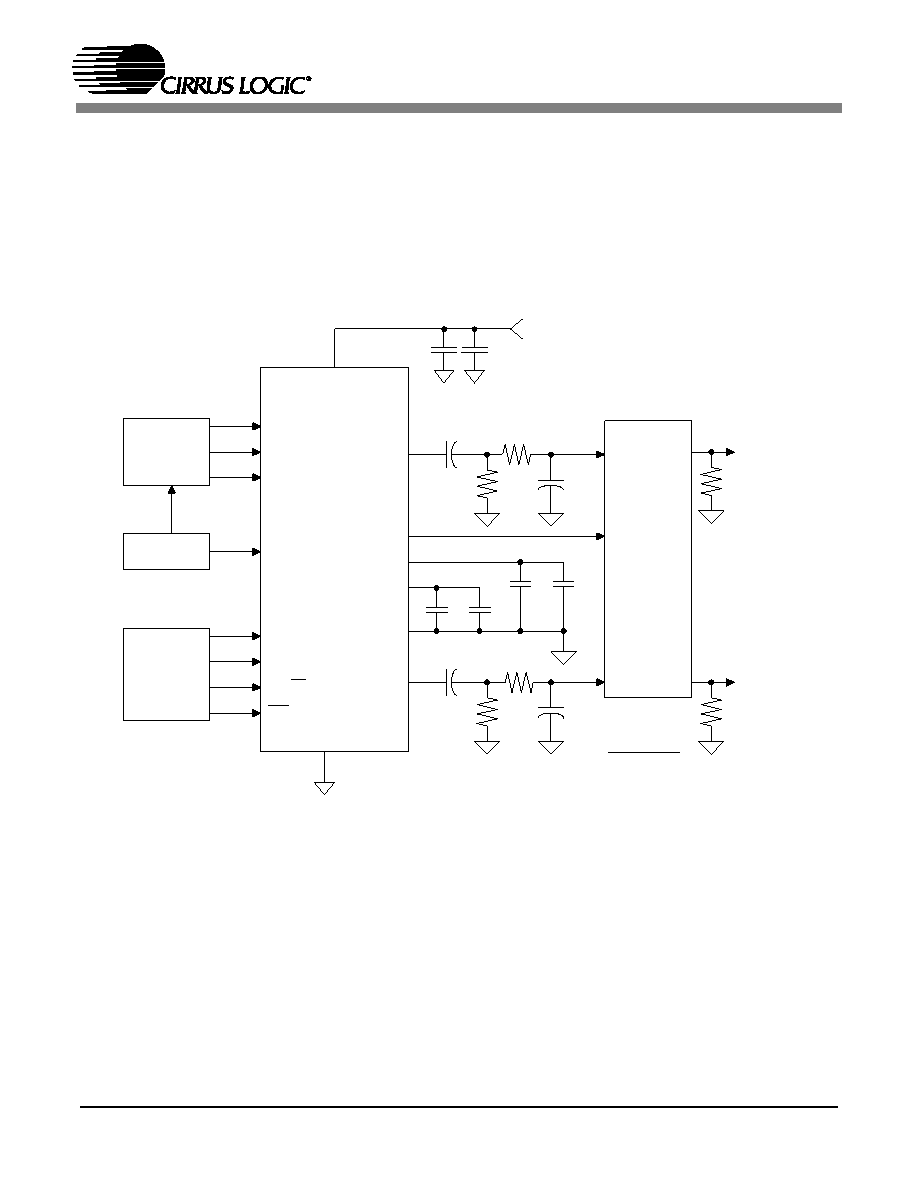

TYPICAL CONNECTION DIAGRAM

13

Serial Audio

Data

Processor

External Clock

MCLK

AGND

AOUTB

CS4341A

SDIN

LRCK

VA

AOUTA

3

4

5

14

0.1 F

+

1F

12

+3.3V or +5.0V

3.3 F

10 k

C

560

560

+

Micro-

Controlled

Configuration

8

6

7

SCLK

1

2

SCL/CCLK

SDA/CDIN

AD0/CS

RST

MUTEC 16

OPTIONAL

MUTE

CIRCUIT

15

1F

0.1 F

Audio

Output A

Audio

Output B

R L

+

10 k

.1 F

1F

9

10

11

REF_GND

FILT+

VQ

C=

4πFs(R 560)

L

R560

L +

Figure 1. Typical Connection Diagram

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS4351-DZZ

IC DAC STER 112DB 192KHZ 20TSSOP

CS4352-DZZ

IC DAC STER 102DB 192KHZ 20TSSOP

CS4354-CSZ

IC DAC 24BIT SRL 14SOIC

CS4360-KZZ

IC DAC STER 6CH 102DB 28TSSOP

CS4361-CZZR

IC DAC STER 6CH 105DB 20-TSSOP

CS4362-KQZ

IC DAC 6CH 114DB 192KHZ 48LQFP

CS4362A-DQZ

IC DAC 6CH 114DB 192KHZ 48-LQFP

CS4364-CQZR

IC DAC 103DB 24BIT 6CH 48-LQFP

相关代理商/技术参数

CS4341A-KSZ

制造商:Cirrus Logic 功能描述:D/A Converter (D-A) IC

CS4341A-KSZ

制造商:Cirrus Logic 功能描述:IC AUDIO DAC 24BIT 192KHZ 101DB

CS4341A-KSZR

功能描述:数模转换器- DAC IC 24-Bit 192 kHz Stereo DAC w/VC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4341-CZZ

功能描述:数模转换器- DAC IC 24bit 96kHz 101dB Stereo DAC w/VC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4341-CZZR

功能描述:数模转换器- DAC IC 24bit 96kHz 101dB Stereo DAC w/VC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4341-KS

功能描述:数模转换器- DAC 24-bit 96kHz 101dB Stereo DAC w/VC

RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4341-KSR

功能描述:数模转换器- DAC 24-bit 96kHz 101dB Stereo DAC w/VC

RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4341-KSZ

制造商:Cirrus Logic 功能描述:24-BIT, 96 KHZ STEREO DAC WITH VOL CNTRL - Bulk 制造商:Cirrus Logic 功能描述:IC DAC 24BIT SRL 96KHZ 16-SOIC 制造商:Cirrus Logic 功能描述:24Bit 96kHz 101dB Stereo DAC